本发明案的锁相环中来自VCO的锁相环输入输出信号及VCO输出信号属于三个不同器件的输出信号,处在锁相环锁定状态下的锁相环外部输入信号与锁相环输出信号呈正交关系,尽管鉴相器即锁相环的二个输入信号依旧保持着鉴相器原有的同步同相关系。有关锁定状态下锁相环的二个输入信号Wr,Wc,输出信号Wout与VCO输出信号Wvco的时序工作关系如图所示,其中锁相环外部输入信号与锁相环输出信号呈正交关系,内中外部输入信号并无等占空比的限制条件,方便说明起见采用了等占空比信号的样例。

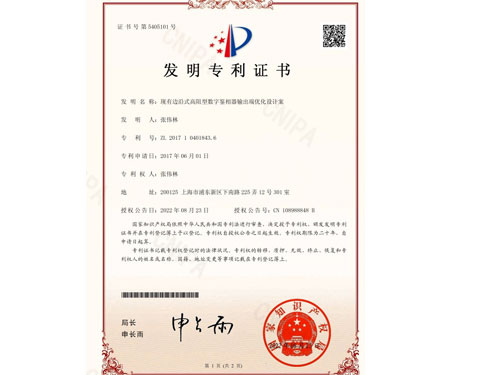

本发明涉及到一种由专利申请号:2017104018436《现有边沿式高阻型数字鉴相器输出端优化设计案》与专利申请号:2019107091998《异质型触发器配组的高阻型数字鉴相器》中的二个边沿式高阻型鉴相器组环锁相环,形成二个锁相环输入信号在锁定时有着正交关系结构电路的设计方法,本发明所涉及的二个鉴相器输入输出信号关系严格依循于二个专利申请件中规定的工作关系。本设计的电路更适合应用在集成化电路设计的锁相环电路中。

本技术中的边沿式高阻型鉴相器限定于专利申请号:2017104018436《现有边沿式高阻型数字鉴相器输出端优化设计案》与专利申请号:2019107091998《异质型触发器配组的高阻型数字鉴相器》中的二个鉴相器,如果需要对鉴相器输入信号的窄时宽化需求则应从采用专利申请号2019103695255:《适合在边沿式鉴相器组环锁相环中应用的二项信号处理技术》中的相对应技术,应用在本件中鉴相器输入输出信号关系严格依循于二个专利申请件中的规定。VCO采用专利申请号:2015106462988《LF内置化高阻型数字鉴相器IC的设计案》中的VCO基本内核结构电路,锁相环结构电路采用专利申请号:2015106451273《全自动锁定工作状态的高阻型数字鉴相器》中的基本内核结构电路。

本发明的设计思想是通过对VCO的输出作二分频,VCO二分频输出作为锁相环的输出信号与输出信号经过时序调整后的信号作为锁相环的一个输入信号,最终实现锁相环的外部输入信号与锁相环的输出信号在锁定状态下的正交化,即采用了VCO输出信号、锁相环输出信号、锁相环输入信号各自分离的概念与技术。

技术领域

背景技术

发明内容